8MHz → 125ns (Period)

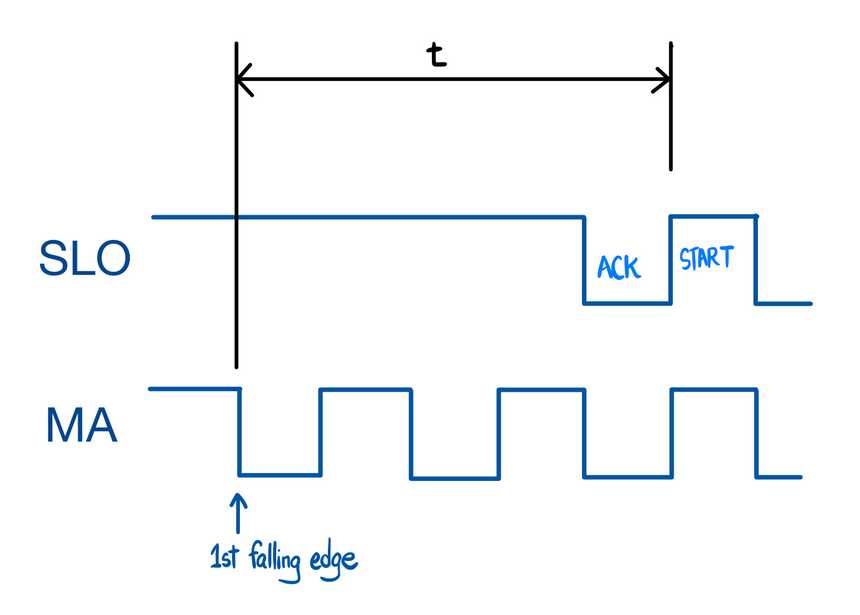

Based on clock/data wave (Link) - Rise/Fall time is ~25ns

In a half-period 125/2 = 62.5ns, 25/62.5 = 40% of the time is unreliable

Additional Line Delay: (2~2.4)*5.208ns/meter = 10.416ns/m ~ 12.5ns/m

From (Renishaw) the line delay is 10ns/m (Very Similar)

New: New method of measuring (Just using a different trigger point)

3M Ethernet Cable

Delay: FPGA 0x67*5.208ns = 536.424ns (0x67=103)

New: 0x59 → 89

5M Ethernet Cable

Delay: FPGA 0x6B*5.208ns = 557.256ns (0x6B=107)

New: 0x5D → 93

10M Ethernet Cable

Delay: FPGA 0x75*5.208ns = 609.336ns (0x75=117)

New: 0x67 → 103

10M+5M Ethernet Cable

Delay: FPGA (0x7F)*5.208ns = 661.416ns (0x7F=127)

New: 0x73 → 115

10M + 5M + 3M Ethernet Cable

Delay: FPGA (0x85)*5.208ns = 692.664ns (0x85 = 133)

New: 0x79 → 121

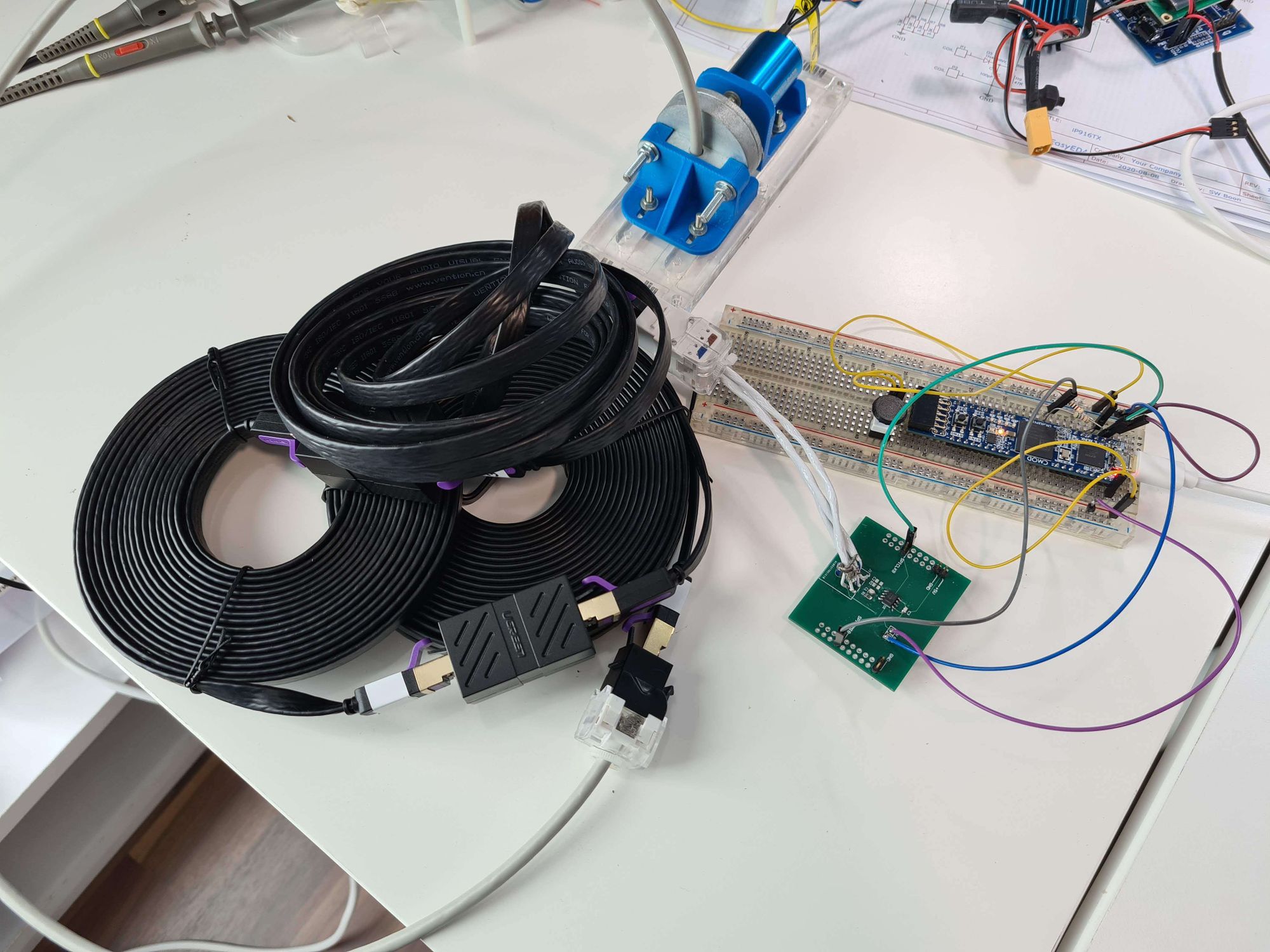

Testing Setup

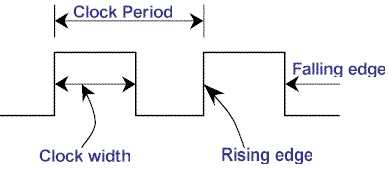

Delay is measured from width:

Resolution: 192MHz → 5.208ns

Physical Setup

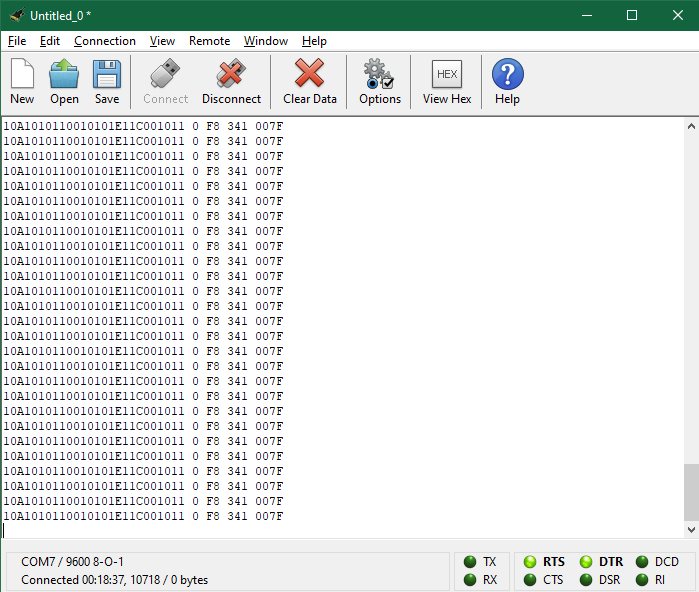

Reading - Acquisition

The sampled data are send back to PC via UART communication

The data to take note is the last 4 character which is the in clock cycle (In this example is 0x007F)

Data Realiability

One set of data has been crosschecked with an logic analyzer running on 24MHz sampling rate and the number match up.

The time doesn't fluctuate during the test (Over thousands of data points) means it is accurate

The relationship between distance are also linear and can be easily use to interpolate the delay at different lengths