`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 11/06/2020 04:15:07 PM

// Design Name:

// Module Name: project3

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module project3(

input clk,

input pio28,

output [3:0] led,

output pio26,

output pio27

);

reg [25:0] count_div67k = 0;

reg [3:0] count_div16 = 0;

reg output_8MHz = 0;

reg output_16MHz = 0;

reg biss_clk = 0;

reg input_flag;

wire clk_192MHz;

wire reset;

assign reset = 0;

//=====LED Output====

assign led[0] = count_div67k[25]; //192MHz / 2^26 = 2.86Hz

//assign led[1] = count_div67k[24];

//assign led[2] = count_div67k[23];

assign led[3] = button_state;

//===================

//=====Digital Outout=====

assign pio26 = interrupt_state;//button_state;//count_div16[3]; //192MHz / 2^4 = 12MHz

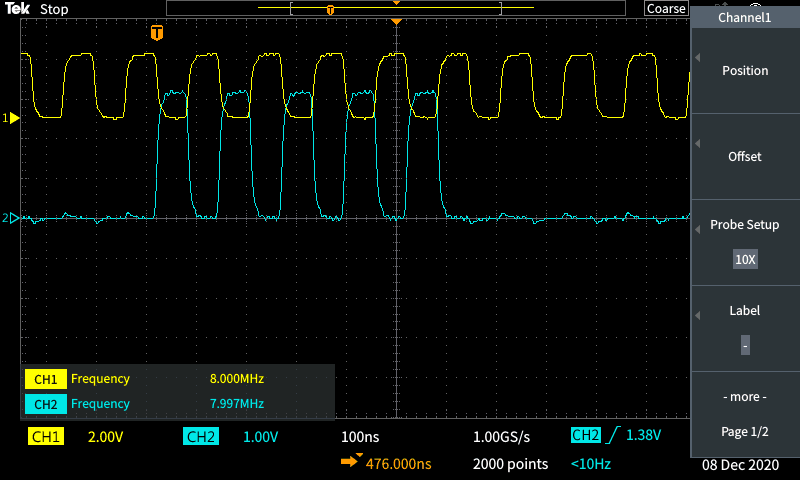

assign pio27 = biss_clk; //8MHz CLK

//========================

reg [3:0] count_8MHz = 0;

reg [3:0] count_16MHz = 0;

always @ (posedge(clk_192MHz)) begin //Trigger at 192MHz

count_div67k = count_div67k + 1;

count_div16 = count_div16 + 1;

count_8MHz = count_8MHz + 1;

count_16MHz = count_16MHz + 1;

if(count_8MHz == 12) begin //Flip at 16MHz

count_8MHz = 0;

output_8MHz = ~output_8MHz;

end

if(count_16MHz == 6) begin //Flip at 32MHz

count_16MHz = 0;

output_16MHz = ~output_16MHz;

end

end

//====Input Debounce===

reg [3:0] debounce_count;

reg pio28_prev_state;

reg button_state;

always @ (posedge (count_div67k[17])) begin //Trigger at 192MHz / 2^18 = 732Hz

if(pio28 != pio28_prev_state) debounce_count = 4'b0;

else if(debounce_count < 4'd15)

begin

debounce_count = debounce_count + 4'b1;

end

else button_state = pio28;

pio28_prev_state = pio28;

end

//=====================

//=========

reg interrupt_state;

reg button_prev_state;

reg [4:0] transmission_count =5'b0;

always @ (posedge output_16MHz) begin

interrupt_state = ~interrupt_state;

if((button_state == 1'b0) && (button_prev_state == 1'b1)) transmission_count = 5'd5; //Set to transmit 10 Pulse

if(output_8MHz == 1'b1) //Posedge

begin

if(transmission_count != 5'd0)

begin

transmission_count = transmission_count - 5'd1; //Pulse Decay

biss_clk = 1'b1;

end

end

if(output_8MHz == 1'b0) //Negedge

begin

biss_clk = 1'b0;

end

button_prev_state = button_state;

end

//=======================

clk_gen_wrapper clk_gen_1(.clk_in1(clk), .clk_out1(clk_192MHz), .reset_in1(reset)); //Output 192MHz Clock

endmodule

Verilog