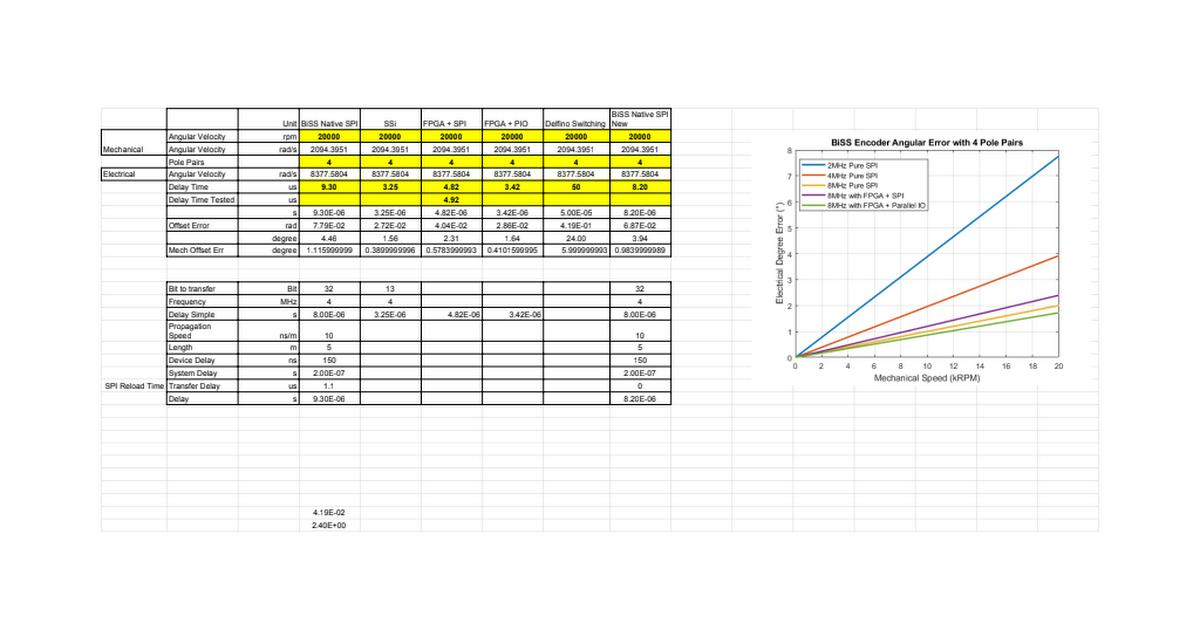

Clock

192MHz → 5.208ns per clock cycle

8MHz → 125ns per clock cycle

4MHz → 250ns per clock cycle

Round Trip Time

4.82us

Notes: Disregard SSi as there is internal ~50us delay

Delfino Reaction Time

Time when Delfino is triggered and CLK start = 2.26us (Measured)

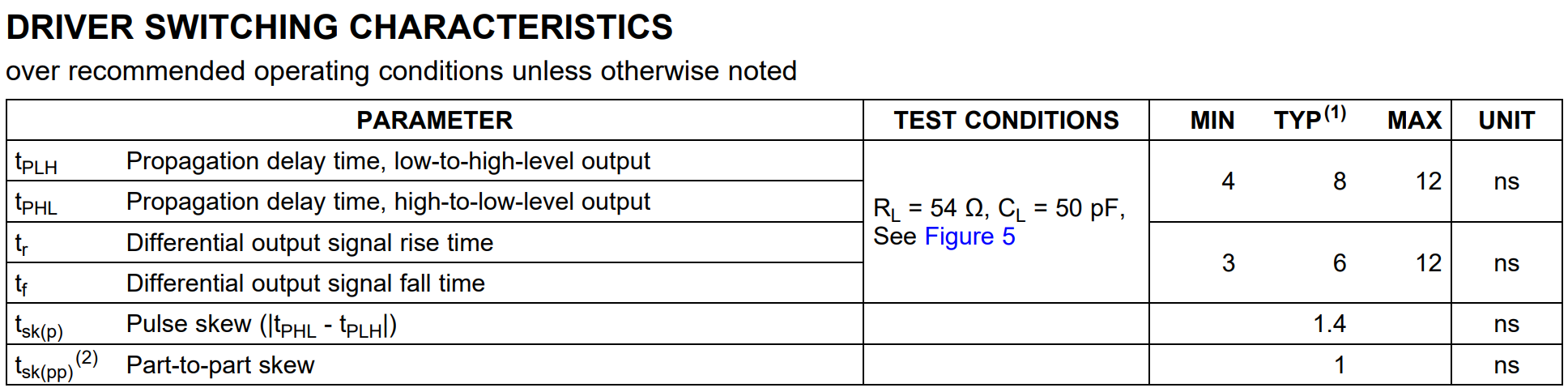

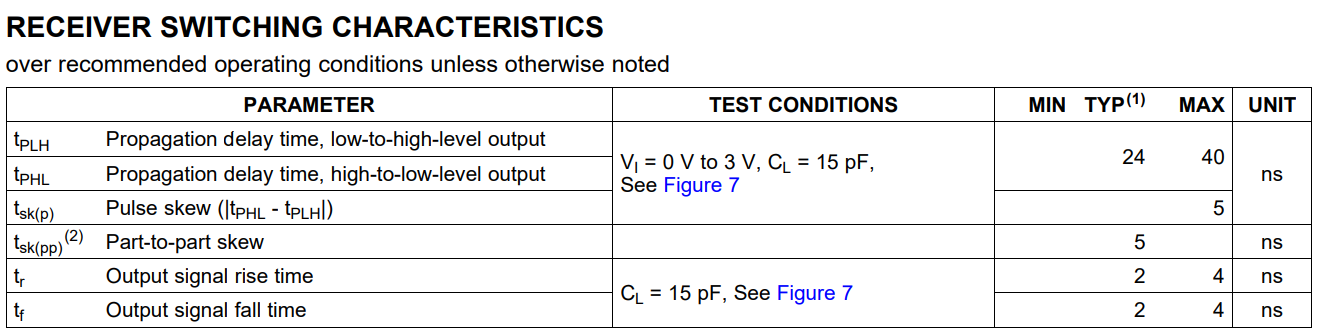

FULL-DUPLEX RS-485/RS-422 Delay

Single Line → Dual Line = 6.8ns (Measured)

Dual Line → Single Line = 30.4ns (Measured)

Refresh Rate of RM44D05

Data: Message period of 27.3125us or 36.613kHz (Delfino)

Message Period = 40kHz (FPGA) (Higher than company specification)

Propagation Delay

Additional Delay: 2*5.208ns/meter = 10.416ns/m

Encoder Delay

~96ns is the system delay

FPGA

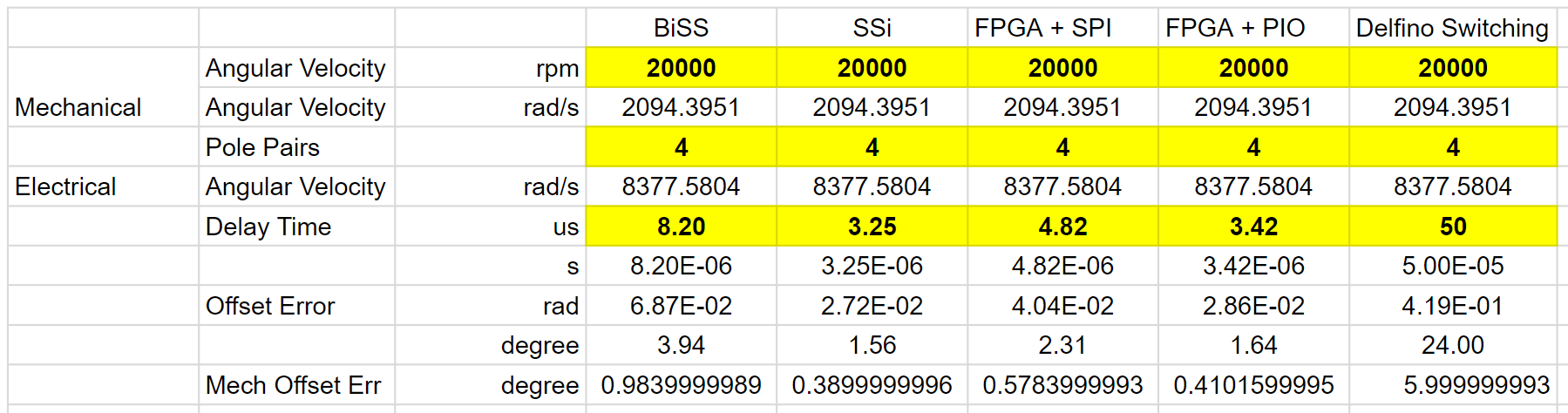

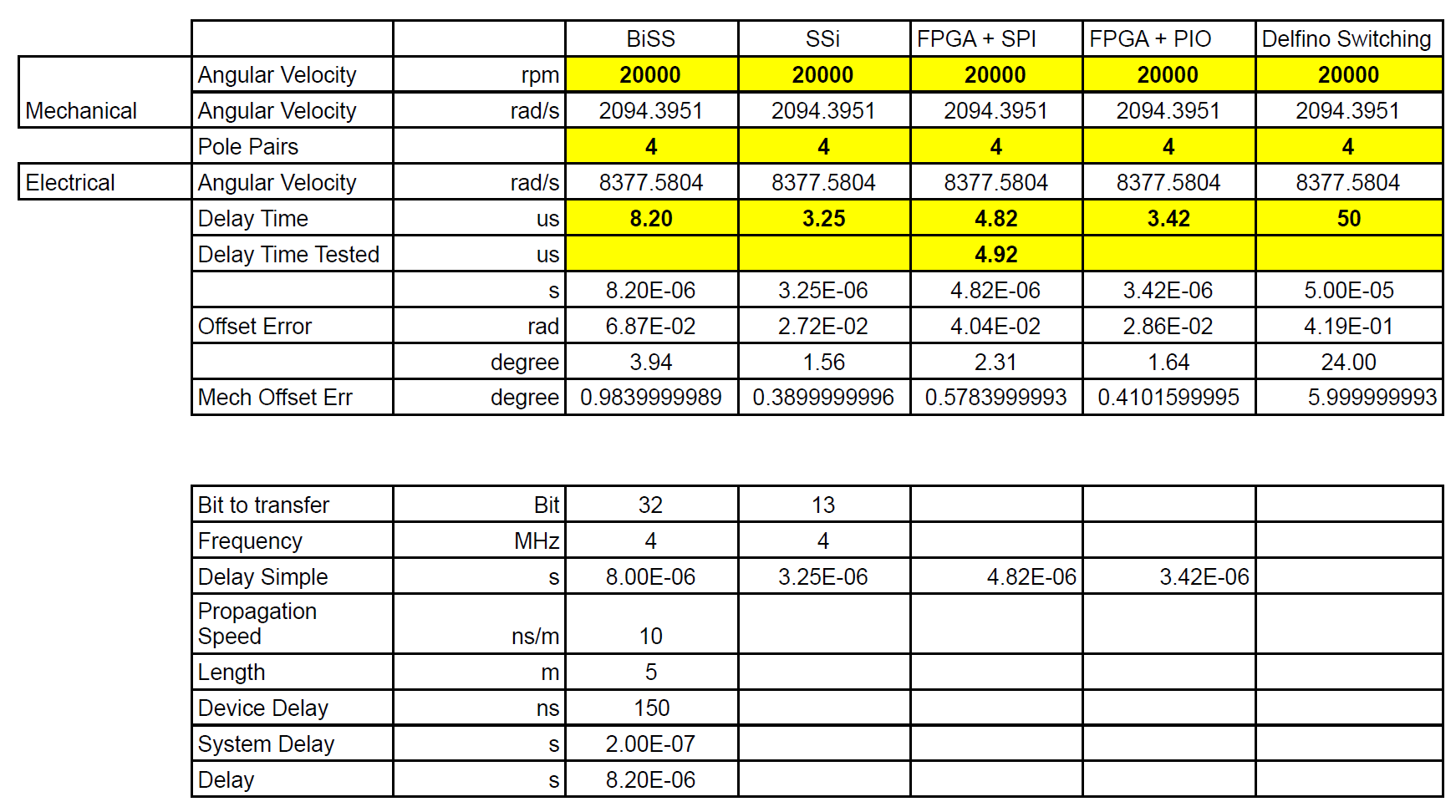

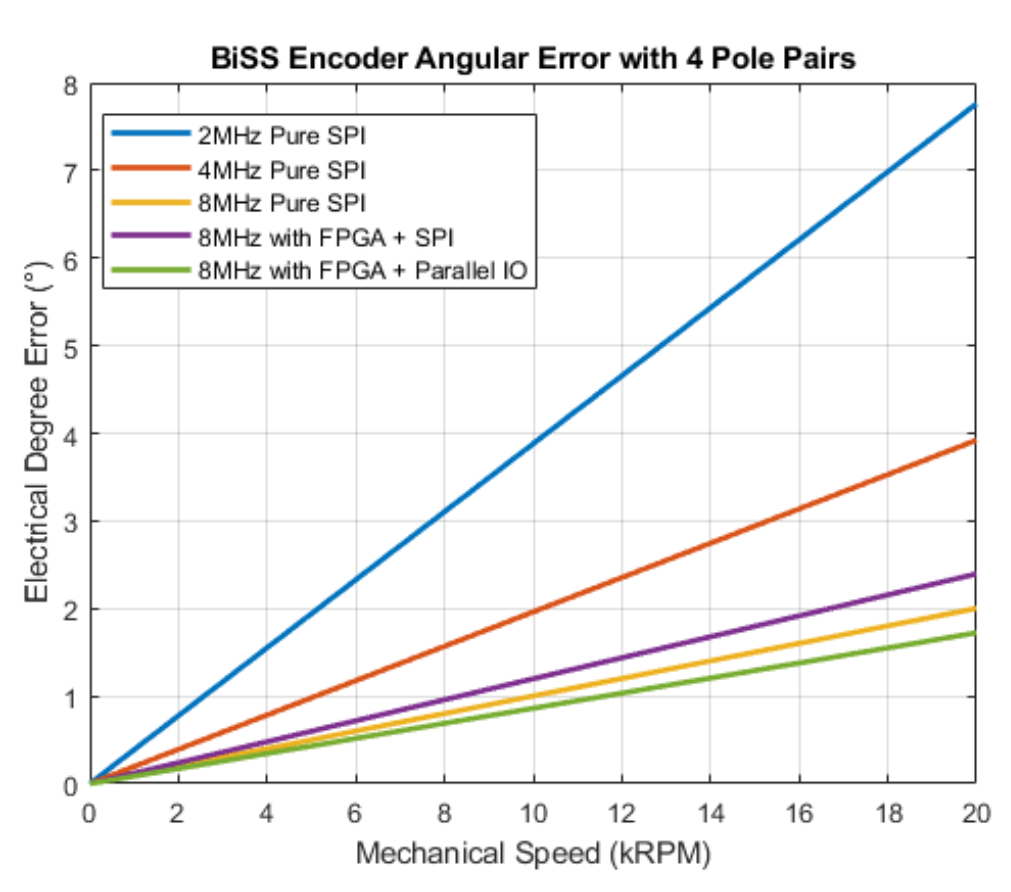

Protocol/Setup Comparison