System Delay (Encoder to Delfino via FPGA)

Legend

0 - Position Sampling Start

A - Latch Position Data

B - Data transferred to FPGA

C - Start transferring to Delfino

D - Data transferred to Delfino

Timing

0 - A: 375~333ns

A - B: 2.62~2.75us (2.875us Theoretically)

B - C: 458~542ns

C - D: 1.375us

Total Time: ~4.912us

Data Latched* to Delfino Received Time: ~4.537us

Logic Analyzer Resolution is 41.667ns

* Data latched measured at FPGA side has a propagation delay of 10.416ns/m

Data Latched(Propagation Delay Compensated @ 5m) to Delfino Received Time:

~4.589us

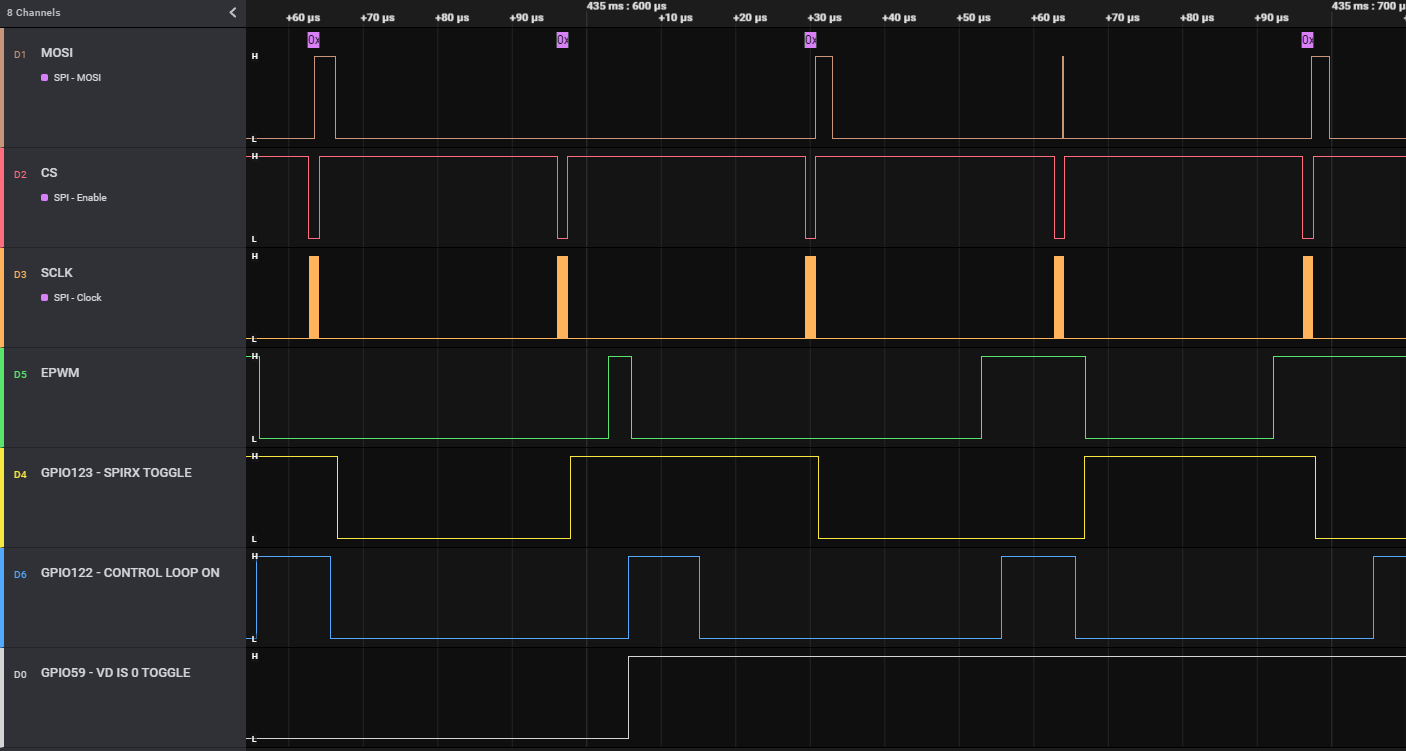

System Delay (SPI Input to ePWM Acting)

Hardware Settings

ePWM Clock - 100MHz

ePWM Period - 2500 (40kHz) - Using triangle wave (Hence 20kHz)

Timing

Control loop time (Open Loop Voltage Mode): ~10us

Position Delay due to unsynchronized sampling: 50us (Max)

SPIRX to start process time: 292ns

Logic Analyzer Resolution is 41.667ns

Delfino ADC Sampling Time

ePWM Set at couter == 0

ADC Start at ePWM == 0

Control loop on after ADC finished sampling

ADCCLK = 200MHz/5 → 40MHz

In 16-bit mode, the core requires approximately 29.5 ADCCLK cycles to process a voltage into a conversion result

//Simulink Generated Code

AdcbRegs.ADCSOC0CTL.bit.ACQPS = 14.0; /* Set SOC0 S/H Window to 15.0 ADC Clock Cycles*/

C++

Time needed == 750ns (30ADCCLK) / 375ns (15ADCCLK)

ePWM == 0 to after ADC sampling is 1us

C Function Runtime

processBissSpiPacket = 0.585us