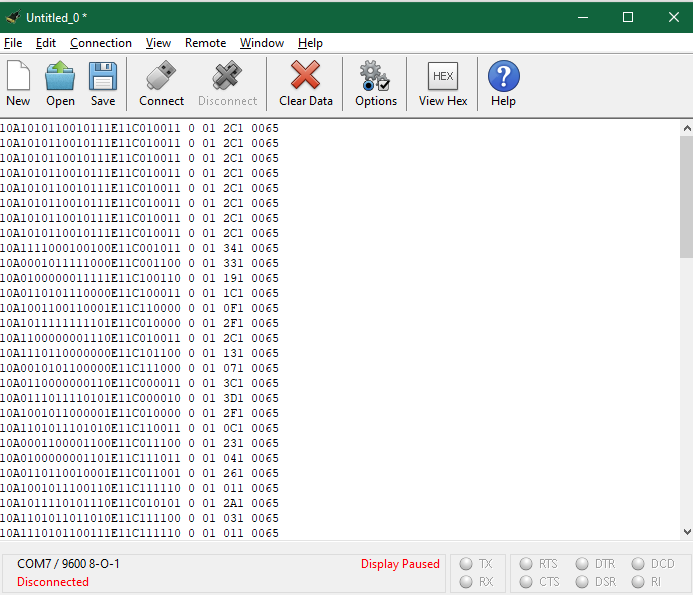

PC Software

UART Software Coolterm →

UART Scope Plotter→

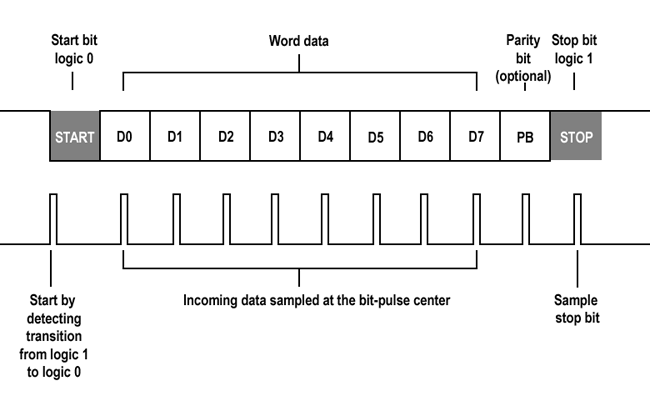

Example Layout (Using Odd Parity Bit)

UART Timing Diagram

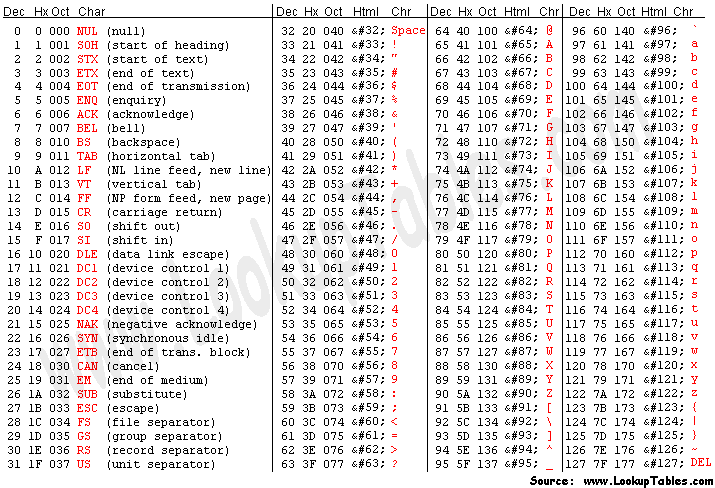

Character Table

Verilog Code for UART (As of 20Dec20)

//=====UART====

reg uart_reset = 1;

reg [7:0] uart_message [0:127];

wire [6:0] message_add;

wire uart_tx_buff;

wire uart_busy;

reg [3:0] uart_setup_state = 0;

reg [5:0] transfer_id_prev = 0;

reg [6:0] uart_message_count = 0;

parameter [7:0] char_zero = 8'd48;

always @(posedge(output_uart_clk)) begin //9600Hz

if((transfer_id != transfer_id_prev) && (ready_to_transfer == 1) && (uart_setup_state == 0)) begin

uart_setup_state = 1;

transfer_id_prev = transfer_id;

uart_message[00] <= biss_message[00] + char_zero;

uart_message[01] <= biss_message[01] + char_zero;

uart_message[02] <= 8'h41; //'A'

uart_message[03] <= biss_message[02] + char_zero;

uart_message[04] <= biss_message[03] + char_zero;

uart_message[05] <= biss_message[04] + char_zero;

uart_message[06] <= biss_message[05] + char_zero;

uart_message[07] <= biss_message[06] + char_zero;

uart_message[08] <= biss_message[07] + char_zero;

uart_message[09] <= biss_message[08] + char_zero;

uart_message[10] <= biss_message[09] + char_zero;

uart_message[11] <= biss_message[10] + char_zero;

uart_message[12] <= biss_message[11] + char_zero;

uart_message[13] <= biss_message[12] + char_zero;

uart_message[14] <= biss_message[13] + char_zero;

uart_message[15] <= biss_message[14] + char_zero;

uart_message[16] <= 8'h45; //'E'

uart_message[17] <= biss_message[15] + char_zero;

uart_message[18] <= biss_message[16] + char_zero;

uart_message[19] <= 8'h43; //'C'

uart_message[20] <= biss_message[17] + char_zero;

uart_message[21] <= biss_message[18] + char_zero;

uart_message[22] <= biss_message[19] + char_zero;

uart_message[23] <= biss_message[20] + char_zero;

uart_message[24] <= biss_message[21] + char_zero;

uart_message[25] <= biss_message[22] + char_zero;

uart_message[26] <= 8'h20; //Space Bar

uart_message[27] <= biss_message[23] + char_zero;

uart_message[28] <= 8'h20; //Space Bar

uart_message[29] <= error_m_sig;

uart_message[30] <= error_l_sig;

uart_message[31] <= 8'h20; //Space Bar

uart_message[32] <= test1;

uart_message[33] <= test2;

uart_message[34] <= crc_validity + char_zero;

uart_message[35] <= 8'h20; //Space Bar

uart_message[36] <= delay_1;

uart_message[37] <= delay_2;

uart_message[38] <= delay_3;

uart_message[39] <= delay_4;

uart_message[40] <= 8'h0D;

uart_message[41] <= 8'h0A;

uart_message[42] <= 8'h00;

end

case(uart_setup_state)

1: begin

uart_reset = 0;

if(uart_busy == 1) uart_setup_state = 2;

end

2: begin

if(uart_busy == 0) begin

uart_setup_state = 0;

uart_reset = 1;

end

end

endcase

end

Uart_transmission trans1(.iClk(output_uart_clk), .iRst(uart_reset), .iMessage(uart_message[message_add]),.oTxUA(uart_tx_buff),.oBusy(uart_busy),.oAdd(message_add));

//=============

Verilog

//======Convert Byte to 2 Char in HEX Form=====

module byte_to_Char(iByte,oCharLHS,oCharRHS);

input [7:0] iByte;

output reg [7:0] oCharLHS,oCharRHS;

always @(*) begin

if(iByte[3:0] >= 10) oCharRHS = iByte[3:0] - 8'd10 + 8'h41;

else oCharRHS = iByte[3:0] + 8'h30;

if(iByte[7:4] >= 10) oCharLHS = iByte[7:4] - 8'd10 + 8'h41;

else oCharLHS = iByte[7:4] + 8'h30;

end

endmodule

//===============================================

module Uart_transmission(iClk,iRst, iMessage, oTxUA, oBusy, oAdd);

input iClk, iRst;

input [7:0] iMessage;

output oTxUA;

output oBusy;

output [6:0] oAdd;

assign oTxUA = uart_tx_buff_f;

assign oAdd = message_count;

assign oBusy = uart_busy;

//=====UART TX=====

reg uart_busy;

reg prev_iRst;

reg[6:0] message_count=0;

reg [3:0] uart_state = 0;

reg uart_tx_buff_f = 1;

reg [7:0] uart_message_buffer;

always @(posedge(iClk)) begin

if(iRst == 1) uart_state = 0;

else if(iRst == 0 && prev_iRst == 1) begin

uart_state = 4'd1;

message_count = 7'd0;

end

case(uart_state)

0: begin //Idle State

uart_tx_buff_f = 1;

uart_busy = 0;

message_count = 7'd0;

end

1: begin //'0' Logic

uart_busy = 1;

uart_tx_buff_f = 0;

uart_message_buffer = iMessage;

message_count = message_count + 1;

uart_state = uart_state+1;

end

2,3,4,5,6,7,8,9: //Send Data

begin

uart_tx_buff_f = uart_message_buffer[uart_state-2];

uart_state = uart_state+1;

end

10: begin //Parity

uart_tx_buff_f = ~^uart_message_buffer; //Odd Parity

uart_state = uart_state+1;

end

11: begin //Stop Bit 1

uart_tx_buff_f = 1;

uart_state = uart_state+1;

end

12: begin

if((iMessage == 8'd0) ||(message_count == 7'd50)) uart_state = 4'd0;

else uart_state = 4'd1;

end

default:

begin

uart_state = 4'd0;

end

endcase

prev_iRst = iRst;

end

//=================

endmodule

Verilog